Layouts of a test chip for evaluating symmetrical and asymmetrical

$ 23.50 · 5 (725) · In stock

Thermal Analysis and Junction Temperature Rise in Multi-Chip Modules - EEWeb

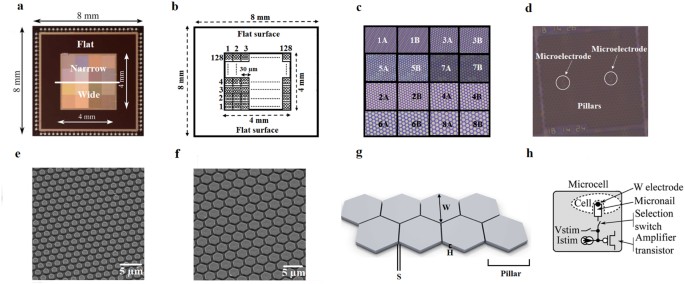

Advantageous environment of micro-patterned, high-density complementary metal–oxide–semiconductor electrode array for spiral ganglion neurons cultured in vitro

a) Whole-chip pin floor plan. Pins in gray are latched pins. Also

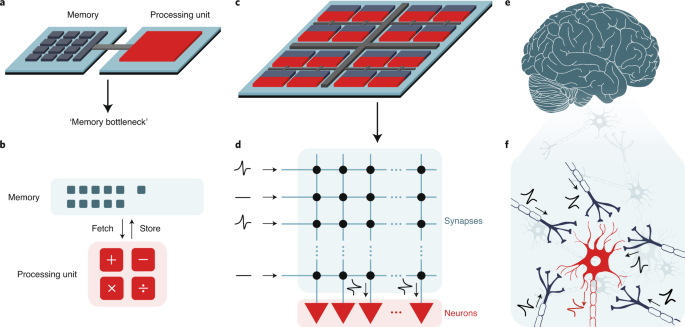

Neuro-inspired computing chips

Simulated field distribution at the wave ports of a GMSL.

Nobuyuki YOSHIKAWA, PhD, Yokohama National University, Yokohama, Department of Physics, Electrical and Computer Engineering

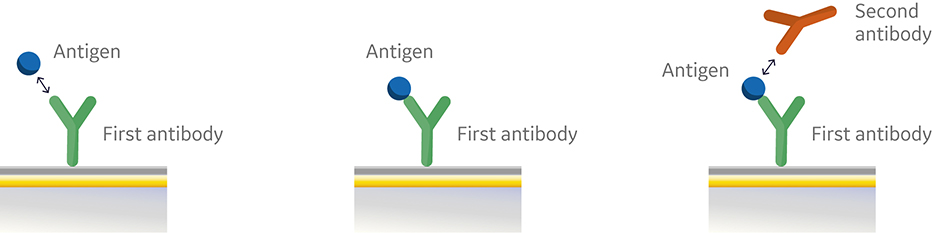

Epitope binning

Strand asymmetries across genomic processes - Computational and Structural Biotechnology Journal

Basic heater layout of Thermal Test Vehicle

a) DL SCA attack set-up on the AES256 with the 65nm test chip; (b, c)

Design for the collision test. (a) Schematic. (b) Initial pollen grain